# **DETERMINATION OF CNTFET OPAMP PARAMETERS**

Sridevi V.1, Jayanthy T.2

<sup>1</sup>Research Scholar, Sathyabama University, Chennai, India <sup>2</sup>Panimalar Institute of Technology, Chennai, India Email: <sup>1</sup>asridevi\_2005@yahoo.com

### **Abstract**

Carbon Nanotube Field Effect Transistor technology is the most promising technology for high speed digital and analog applications. This paper mainly focused on designing an operational amplifier using Carbon Nanotube Field Effect Transistor (CNTFET), since opamp is a widely used core element for analog and mixed signal systems. The various opamp parameters such as dc offset voltage, phase margin, common mode rejection ratio, slew rate etc have been determined and tabulated. The proposed CNTFET opamp exhibit significant improvements in speed and other major opamp parameters over the conventional opamp.

Key words: CNTFET, CMRR, Differential Gain, Opamp, Slew Rate, Phase Margin.

#### I. INTRODUCTION

For many years MOSFET has been used as a basic element of circuit designing [1]. As the miniaturization of silicon based circuits reaches its physical limitations, molecular devices are becoming hopeful alternatives to the existing silicon technology [2],[3]. Carbon nanotubes offer a technology with an exciting solution to the scaling issues of transistors and interconnects and with the possibility of coexistence in the present silicon technology. CNTFETs are novel devices that are expected to sustain the transistor scalability while increasing its performance.

In this paper for CNTFET-based circuits, a compact SPICE model, including non-idealities proposed in [4],[5] with physical parameter variations, has been used for simulations. This standard model has been designed for unipolar, MOSFET-like CNTFET devices, in which each transistor may have one or more CNTs. This model also considers Schottky Barrier Effects, Parasitics, including CNT, Source/Drain, and Gate resistances and capacitances, and CNT Charge Screening Effects. Analog devices require linearity, and it has been demonstrated that CNTFETs have the potential to provide linearity well beyond what is possible with silicon semiconductors [6]–[10].

Nowadays CNTFET technology has become dominant over conventional CMOS technology for analog circuit design in a mixed signal system due to the industry trend of applying standard process technologies to implement both analog and digital circuits on the same integrated chip. Operational amplifier is the widely used core element for analog

and mixed signal systems. A high performance opamp is characterized by a high open loop gain, high bandwidth, very high input impedance, low output impedance and an ability to amplify differential mode signals to a large extent and severely attenuate common mode signals. Many literature exists on the simulation or measurement of frequency dependent operational amplifier characteristics such as open loop gain, common mode gain, common mode rejection ratio (CMRR), power supply gain and power supply rejection ratio (PSSR) [11]–[21].This paper presents the simulation and analysis of high performance CNTFET opamp circuit to point at the optimum topology when CNTFETs are used with special emphasis on low power applications.

This paper is organized as follows: section II introduces the structure and modeling aspects of CNTFET. Section III deals with CNTFET operational amplifier circuit. Simulation and analysis of various opamp parameters such as dc offset voltage, phase margin, common mode rejection ratio, slew rate etc have been made in section IV. Finally in section V, the research paper has been concluded with the work undertaken in this research work and the scope for improvement of the circuit level transistor models.

# II. CARBON NANOTUBE FIELD EFFECT TRANSISTOR

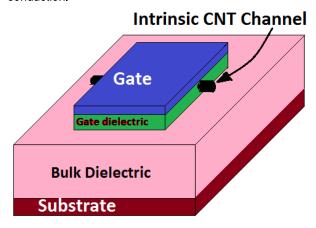

It has been shown that semiconducting carbon nanotubes can be used as the conducting channel in Carbon nanotube field effect transistors. To create such devices, nanotubes are grown on top of a thick silicon dioxide. When metal contacts are laid along the length

of a nanotube, many transistors are formed along CNT. The length of the nanotube, between two contacts, acts as the channel of a transistor with metal source and drain. Because of the fixed CNT diameter once a nanotube is grown, the width of the nanotube cannot be changed to increase the current drive, instead, a transistor's width and current drive can be increased by adding nanotubes in parallel.

The metal gate is used to modulate the electronic band structure of the source, drain and carbon nanotube through a thin gate oxide. The metal gate and oxide must overlap slightly with the source and drain contacts. This overlap limits the area savings of CNTFETs. The current is regulated by the gate to source and gate to drain interactions. Fig.1 is a theoretical illustration of a carbon nanotube FET structure. The structure resembles that of a MOSFET [22]-[24], but the nanotube is the channel for conduction.

Fig. 1. Structure of MOSFET like CNTFET

#### III. CNTFET OPERATIONAL AMPLIFIER

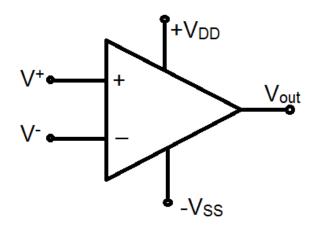

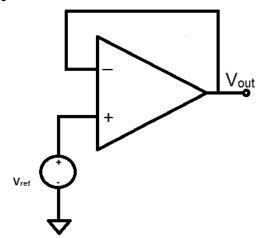

Opamps are the functional core element of many mixed analog and digital VLSI systems especially in interface circuits such as analog to digital converters, digital to analog converters, switched capacitor filters etc. Fig. 2 shows the schematic of ideal opamp and ideal opamp parameters are shown in Table 1.

Table 1: Ideal opamp parameters

| Parameter         | Value |

|-------------------|-------|

| Gain              | α     |

| Input Resistance  | α     |

| Output Resistance | 0     |

| CMRR              | α     |

Fig. 2. Schematic of Ideal Opamp

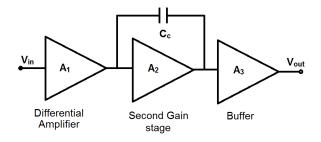

The CNTFET operational amplifier comprises of three functional building blocks as shown in Fig.3.

Fig. 3. Functional Blocks of CNTFET Opamp

First block is the differential amplifier block forms the input of the opamp and provides a good overall gain to improve noise and offset performance. The second gain circuit block is configured as a simple common source stage so as to allow maximum output swings. The last block is the buffer circuit to convert high input impedance of the second gain stage to low output impedance and provides current gain. Capacitor  $C_c$  is included in the circuit to ensure stability when the opamp is used with feedback and used to lower the gain at higher frequencies thereby used as a compensating device.

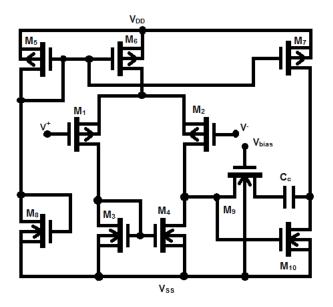

The proposed CNTFET opamp circuit is shown in Fig. 4.

The circuit will provide good voltage gain, a good common mode range and good output swing. The first stage in Fig.4 consists of a p-channel differential pair  $M_1 - M_2$  with an n-channel current mirror load  $M_3 - M_4$  and a p-channel tail current source  $M_6$ . The

Fig. 4. CNTFET Opamp Circuit

second stage consists of an n-channel common source amplifier  $M_{10}$  with a p-channel current source load  $M_7$ . The high output resistances of these two CNTFETs equate to a relatively large gain for this stage and an overall moderate gain for the complete amplifier. Because the opamp inputs are connected to the gates of CNTFETs, the input resistance is essentially infinite when the amplifier is used in internal applications.

### IV. RESULTS AND DISCUSSIONS

In this paper Stanford models of CNTFET have been used for simulations and evaluation of opamp performance parameters using HSPICE. Top gated undoped semiconducting CNTFETs have been used for design and analysis of the proposed opamp. The various op amp parameters such as dc offset voltage, CMRR, input and output resistances, phase margin etc have been determined using Hspice simulations.

## A. Determination of dc offset voltage

Input dc offset voltage is defined as the voltage that must be applied between the inverting and non inverting input terminals of the opamp to obtain zero volts at the output and is abbreviated as  $V_{os}$ . The cause of input offset voltage is due to the inherent mismatch of the input transistors and components during the fabrication of the die and the stress placed on the die during the packing process. All these effects together produce a mismatch of the bias currents that flow through the input circuit and resulting in a

differential voltage at the input terminals of the opamp. Audio amplifiers, communications circuits and converters often use ac-coupling to remove  $V_{\rm os},$  many devices such as data converters, processors and CMOS chopper amplifiers correct the offsets internally and some devices particularly instrumentation amplifiers and opamps in single packages, have external pins where  $V_{\rm os}$  can be externally reduced.

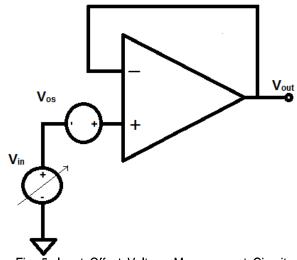

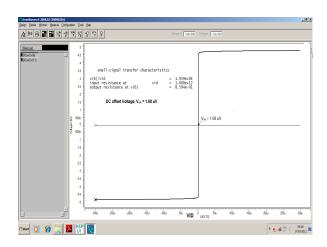

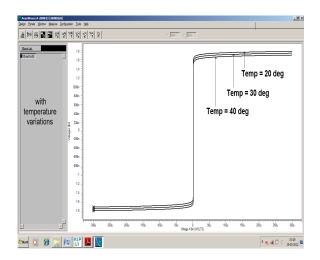

Fig.5. shows unity gain feedback opamp circuit for measurement of input offset voltage. Fig.6 shows the response of CNTFET opamp without input offset voltage compensation and Fig.7 shows the response of the opamp for variation in temperature. The main advantage of the CNTFET used is that it can be operated with a supply voltage of less than 0.5V leads to low power dissipation.

Fig. 5. Input Offset Voltage Measurement Circuit

Fig. 6. Response of Opamp Without Input Offset Voltage Compensation

From Fig.6 the following opamp parameters have been determined,

DC offset Voltage,  $V_{os} = 1.68 \, uV$

Differential Gain,  $A_{vd} = 1.959E + 4$

Power Dissipation = 3.91 mW

Fig. 7. Response of Opamp for Temperature Variations

#### B. Determination of CMRR

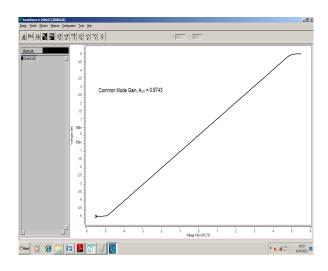

Fig.8 shows the non inverting unity gain opamp circuit for measurement of input common mode range. Fig.9 shows the response of the opamp for variations in the common mode voltage. The common mode gain,  $A_{cm}$  obtained through simulation is 0.9743.

Fig. 8. Input CMR Voltage Measurement Circuit

The Common Mode Rejection Ratio (CMRR) of an opamp measures the tendency of the device to reject input signals common to both inverting and non inverting input leads. CMRR can be calculated as follows.

CMRR =

$$\frac{A_{Vd}}{A_{cm}} = \frac{1.959E + 4}{0.9743} = 20106.74$$

CMRR in

$$dB = 20 \log \left( \frac{A_{Vd}}{A_{cm}} \right) = 86 dB$$

Fig. 9. Input common mode range simulation

# C. Determination of Frequency Response Characteristics

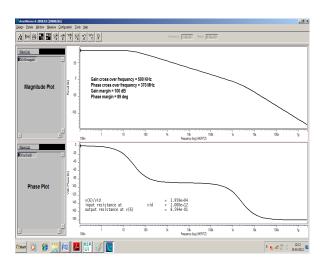

Fig.10 shows the frequency response of CNTFET opamp. The major AC parameters of the opamp such as phase margin, gain margin, gain cross over frequency and phase cross over frequency can be determined using frequency response characteristics. From the response characteristics,

Gain crossover frequency = 500 KHz

Phase crossover frequency= 380 MHz

Gain Margin = 100 dB

Phase Margin  $= 89 \deg$

3 dB gain = 86 - 3 = 83 dB

Fig. 10. Frequency response of CNTFET opamp

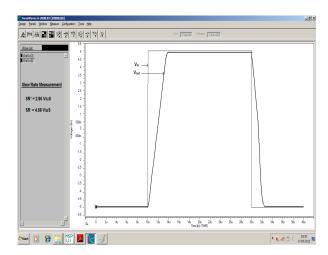

# D. Determination of Slew Rate

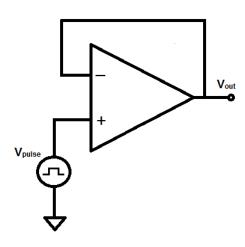

If the amplitude of the input step is steadily increased, a point is reached at which the output become slew rate limited and the initial portion of the transient curve becomes a linear ramp, the slope of which is called the slew rate (SR). Fig.11 shows the circuit to visualize slew rate and the result is shown in Fig.12.

Fig. 11. Slew Rate Measurement Circuit

The positive slew rate SR + is the slope of the rising edge of the output which can be computed from the two points on the rising edge as follows,

$$SR^+ = \frac{4.21 + 4.11}{13.3 - 10.4} = 2.86 \ V/uS$$

The negative slew rate SR- is the slope of the trailing edge of the output which can be computed from the two points on the trailing edge as follows

$$SR = \frac{-3.42 - 4.54}{31.8 - 30.1} = -4.68 \text{ V/uS}$$

Fig. 12. Characteristics for Slew Rate Measurement

Table 2 shows the various parameters values of CNTFET opamp obtained through Hspice simulations.

**Table 2: CNTFET Opamp Parameters**

| Parameter                          | Value         | Unit |

|------------------------------------|---------------|------|

| Dc Offset Voltage, Vos             | 1.68          | uV   |

| Differential Gain, A <sub>vd</sub> | 1.959e4       | -    |

| Common Mode Gain, A <sub>cm</sub>  | 0.9743        | ı    |

| Power Dissipation                  | 3.91          | mW   |

| CMRR                               | 86            | dB   |

| Positive Slew Rate, SR+            | 2.86          | V/uS |

| Negative Slew Rate, SR             | <b>- 4.68</b> | V/uS |

| 3 dB Gain                          | 83            | dB   |

| Phase Margin                       | 89            | deg  |

### V. CONCLUSION

This paper explores basic building block of analog circuits, the operation amplifier using newly emerging CNTFET technology. Circuit characterization was performed for the determination of opamp parameters. The CNTFET opamp exhibit significant

improvement in the opamp parameters compared to traditional opamps and also another advantage of CNTFETs used for designing opamp is that it can be operated with a supply voltage of less than 0.5V leads to low power dissipation. Many modifications and additions can be undertaken to improve opamp system design.

#### **REFERENCES**

- [1] Mojtaba Jamalizadeh et al., 2010, Five new MVL current mode differential absolute value circuits based on carbon nano-tube field effect transistors (CNTFETs), Nano-Micro letters, 2(4), pp.227-234.

- [2] Joerg Appenzeller et al., 2002, Carbon Nanotube Electronics, IEEE Trans. on Nano Technology, pp. 184 –189.

- [3] T. Dang, L. Anghel and R. Leveugle, 2006, CNTFET Basics and Simulation, in proceeding of IEEE International conference on Design and Test of Integrated Systems in Nanoscale Technology, pp. 28-33.

- [4] J. Deng and H.-S P. Wong, 2007, A Compact SPICE Model for Carbon Nanotube Field Effect Transistors Including Non-Idealities and Its Application — Part I: Model of the Intrinsic Channel Region, IEEE Transactions on Electron Devices, 54, 3186.

- [5] J. Deng and H.-S P. Wong, 2007, A Compact SPICE Model for Carbon Nanotube Field Effect Transistors Including Non-Idealities and Its Application — Part II: Full Device Model and Circuit Performance Benchmarking, IEEE Transactions on Electron Devices, 54, 3195.

- [6] Amlani et al, 2009, Measuring Frequency Response of a. Single Walled Carbon Nanotube Common-Source Amplifier, IEEE Transactions on Nanotechnology, 8(2), pp.226-233.

- [7] N. Patil et al, 2009, Circuit-Level Performance Benchmarking and Scalability Analysis of Carbon Nanotube Transistor Circuits, IEEE Transactions on Nanotechnology, 8(1), pp. 37-45.

- [8] F.A. Usmani and M. Hasan, 2009, Design and Parametric Analysis of 32nm OPAMP in CMOS and CNFET Technologies for Optimum Performance, Proceedings of the Argentine School of Micro-Nanoelectronics Technology and Applications, pp 87-92.

- [9] J. Deng et al, 2007, Carbon Nanotube Transistor Circuits: Circuit-Level Performance Benchmarking and Design Options for Living with Imperfections, IEEE Solid State Circuits Conference, pp. 1159-1164.

- [10] J. Guo, S. Datta, and M. Lundstrom, 2002, Assessment of Silicon MOS and Carbon Nanotube FET Performance Limits Using a General Theory of Ballistic Transistors, IEEE International Electron Devices Meeting (IEDM), pp. 711- 714.

- [11] W. M. C. Sansen, M. Steyaert, and P. J. V. Vandeloo, 1985, Measurement of operational amplifier characteristics in the frequency domain, IEEE Trans. on Instrumentation and Measurement., 34(1), pp. 59–64

- [12] K. Higuchi and H. Shintani, 1987, New measurement methods of dominantpole-type operational amplifier parameters, IEEE Trans. Industrial Electronics, 34(3), pp. 357–365.

- [13] S. S. Awad,1990, A simple method to estimate the ratio of the second pole to the gain-bandwidth product of matched operational amplifiers, IEEE Trans. Instrumentation and Measurement, 39, pp. 429–432.

- [14] S. Natarajan, 1991, A simple method to estimate gain-bandwidth product and the second pole of the operational amplifiers, IEEE Trans. Instrumentation and Measurement, 40, pp. 43–45.

- [15] S. Porta and A. Carlosena, 1996, On the experimental methods to characterize the opamp response: A critical view, IEEE Trans. Instrumentation and Measurement, 43, pp. 245–249.

- [16] G. Giustolisi and G. Palumbo, 2002, An approach to test open-loop parameters of feedback amplifiers, IEEE Trans. Circuits and Systems, 49(1), pp.70–75.

- [17] R. Pallás-Areny and J. G.Webster, "Common mode rejection ratio in differential amplifiers," IEEE Trans. Instrum. Meas., vol. 40, pp. 669–676, June 1991.

- [18] M. E. Brinson and D. J. Faulkner, 1995, New approaches to measurement of operational amplifier common-mode rejection ratio in the frequency domain, Proc. Inst. Elect. Eng. Circuits Devices Syst., 142(4), pp. 247–253.

- [19] G. Giustolisi, G. Palmisano, and G. Palumbo, 2000, CMRR frequency response of CMOS operational transconductance amplifiers, IEEE Trans. Instrumentation and Measurement, 49, pp. 137–143.

- [20] M. S. J. Steyaert and W. M. C. Sansen, 1990, Power supply rejection ratio in operational transconductance amplifiers, IEEE Trans. Circuits and Systems, 37, pp. 1077–1084.

- [21] M. E. Brinson and D. J. Faulkner, 1995, Measurement and modeling of operational amplifier power supply rejection, Int. J. Electronics, 78(4), pp. 667–678.

- [22] J. Appenzeller et al., 2002, Field-modulated carrier transport in carbon nanotube transistors, Physical Review Letters, 89(12), pp. 126 801-1–126 801-4.

- [23] Jason Clifford, D. L. John, and David L. Pulfrey, 2003, Bipolar Conduction and Drain-Induced Barrier Thinning in Carbon Nanotube FETs, IEEE Trans. on Nano Technology, pp. 181 –185.

- [24] D. L. John et al., 2003, Electrostatics of coaxial Schottky-barrier nanotube field-effect transistors', IEEE Trans. Nanotechnology, 2, pp. 175–180.

Sridevi V. received her B.E. degree in Electrical and Electronics Engineering from Bharathidasan University, Trichy, India in 1999 and her Power M.E degree in Systems from Anna University, Chennai, India, in 2005. She is currently working for her Ph.D. degree

in Department of Electronics and communication engineering at Sathyabama University, Chennai, India. Her present area of research interests includes modeling and analysis of Carbon Nanotube Field Effect Transistor based circuits, Nano high speed devices and circuits. She is a life time member of Indian Society for Technical Education (ISTE).

Jayanthy T. received her doctorate degree in the field of Microwaves in Sathyabama University in 2007, B.E degree in Electronics and communication Engineering in 1990 and M.E degree in Microwaves and optical Engineering in 1993 from

Madurai Kamaraj University.

She has more than 18 years teaching experience. She was working as a Professor in Electronic and communication department in Sathyabama University. At present she is working as a principal in Panimalar Institute of Technology, Chennai. She has published several papers in international/national journal and conferences. She has published three books named as Microwave Engineering, optical Engineering and transmission lines and waveguides.

Dr.Jayanthy became a fellow of IETE, life member of Society of EMC Engineers and a life member of Indian science congress Association. Her field of interest is Electromagnetics, Microwaves and Antennas.